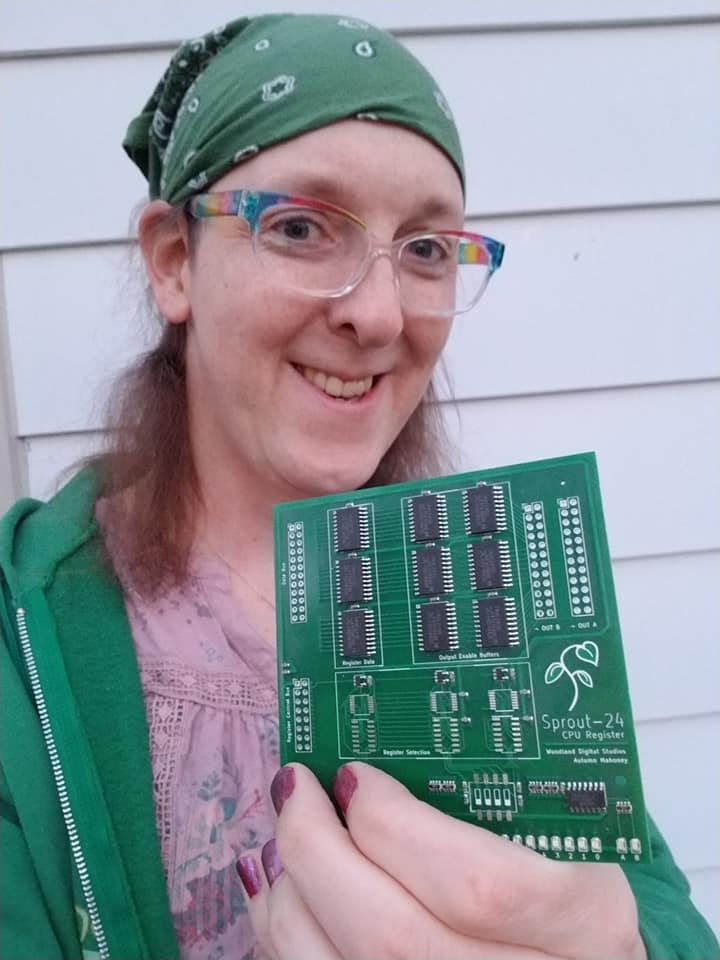

Sprout24 CPU

Sprout24 is a "know-your-roots" computer processor — designed and built from the ground up as a teaching tool to help introduce the basics of computer science and demystify how computing works.

At this point, the CPU is largely completed and running programs, but I'm doing extensive testing and working out the last few bugs. I debuted the project publicly with a presentation at Penguicon 2024 in Ypsilanti, Michigan. Thanks to everyone who showed up and geeked out with me!

~ Autumn

Some new goodies:

Try out this interactive adder simulator that will be part of the learning materials I'm planning to put together.

Or try 🌱 this web game 🌱 the kiddos and I made for you!

Project Log (for all you delightfully geeky friends!)

April 26, 2024 — I'm so excited! The presentation at Penguicon went really well, and I got to geek out with a bunch of people about this project. This was something I've been looking forward to for years. 🩵🐧🐧🐧🩵March 31, 2024 — #GlobalTalk has been a nice distraction, but back to the CPU project now. Tonight I tested my bodge for the Carry flag issue, and it works! This was a hard one to track down because I later discovered a different Carry flag bug in the emulator, so I was troubleshooting against a target that had its own issue. They're finally both working right and agreeing with each other now. The adder simulator I shared last week proved useful for testing and making sure all cases were doing what they should. With that resolved, I'm also seeing that it was masking a different issue that has something to do with the memory address bus getting unexpected values in some situations. I am not sure yet what is going on there, but it seems to have something to do with the stall cycle after a load/store/push/pop. I at least have some test programs that will reliably trigger the mismatch, so hopefully I can track that down soon.

March 20, 2024 — The Status Register is now bodged to use the inverted clock, and the proper Z and S flags are getting latched perfectly now. I'll make a revised Southeast board to make that change permanent. The Carry flag issue is all that is left, and I already know how to fix that, so next I'm going to find a way to bodge that fix in for testing before committing to a new ALU Core board.

March 17, 2024 — I figured out the Carry flag mismatches on some subtractions. They will take a few extra logic gates to fix, so will likely mean a new ALU Core board. Also, I may need to invert the clock on the Status Register to keep its timing from having a propagation race (I guess "hold violation" is the right term).. That may mean a new Southeast board, but I can probably bodge it off the inverted clock on the Register File for now.

March 15, 2024 — The new Control Unit and Register File boards are installed. And the emulator's main loop got a major overhaul that solves the emulator/hardware synchronization in a much more elegant way. It's much easier to interpret testing results now. With that testing, I found that the changes I designed into these two new boards worked exactly how I wanted them to. I can tell that the hardware is much closer now, since the only errors I was able to find were some mismatches in C and S status flags. It seems to have something to do with the invert bit in the instruction, and I have isolated some good test cases that I think will help me pinpoint it. Crucially, I'm not seeing any mis-jumps anymore except for the ones that are correctly responding to the flawed state of the status bits.

March 1, 2024 — While I'm waiting on the PCB order, I've started in on some of the documentation and teaching materials to go along with this project. I've registered sprout24.net to use as the dedicated home for all of that and move things off the main Woodland Digital site. For now, I'll continue with this project log until a more permanent site is ready to launch.

February 29, 2024 — The new Control Unit and Register Files are ordered. Plus, since we really don't need a constant r1 register anymore, I redesigned the Register01 board into just a Register0 board and ordered that too. That'll free up one more general-purpose register for use. With that change, and swapping the opcodes for JMP and JX to make the Control Unit logic cleaner, I had to update the emulator and assembler, and reassemble all of the existing test programs.

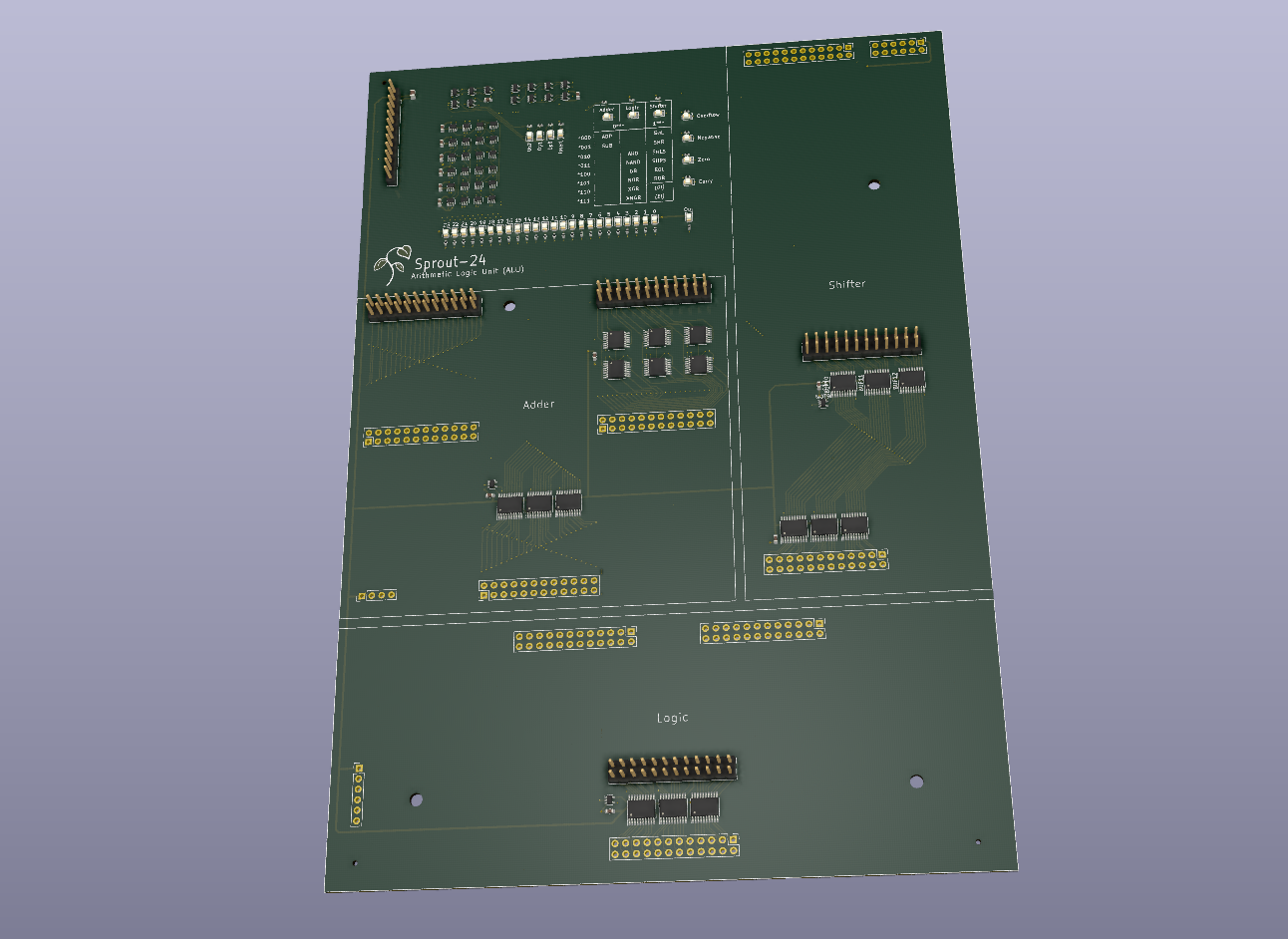

January 28, 2024 — Turns out the value of what the carry flag should be during a subtraction is not well-defined:

"While the carry flag is well-defined for addition, there are two ways in common use to use the carry flag for subtraction operations: ... subtract with borrow ... and subtract with carry".

I'm seeing occasional mismatches of the carry flag between my CPU and emulator, only happening on some subtractions. I suspect I may have implemented it one way in the ALU hardware and the other way in the emulator without realizing it. If that turns out to be the case, then either way is valid, so I can just update the emulator to match the physical ALU and document the behavior in the ISA docs.

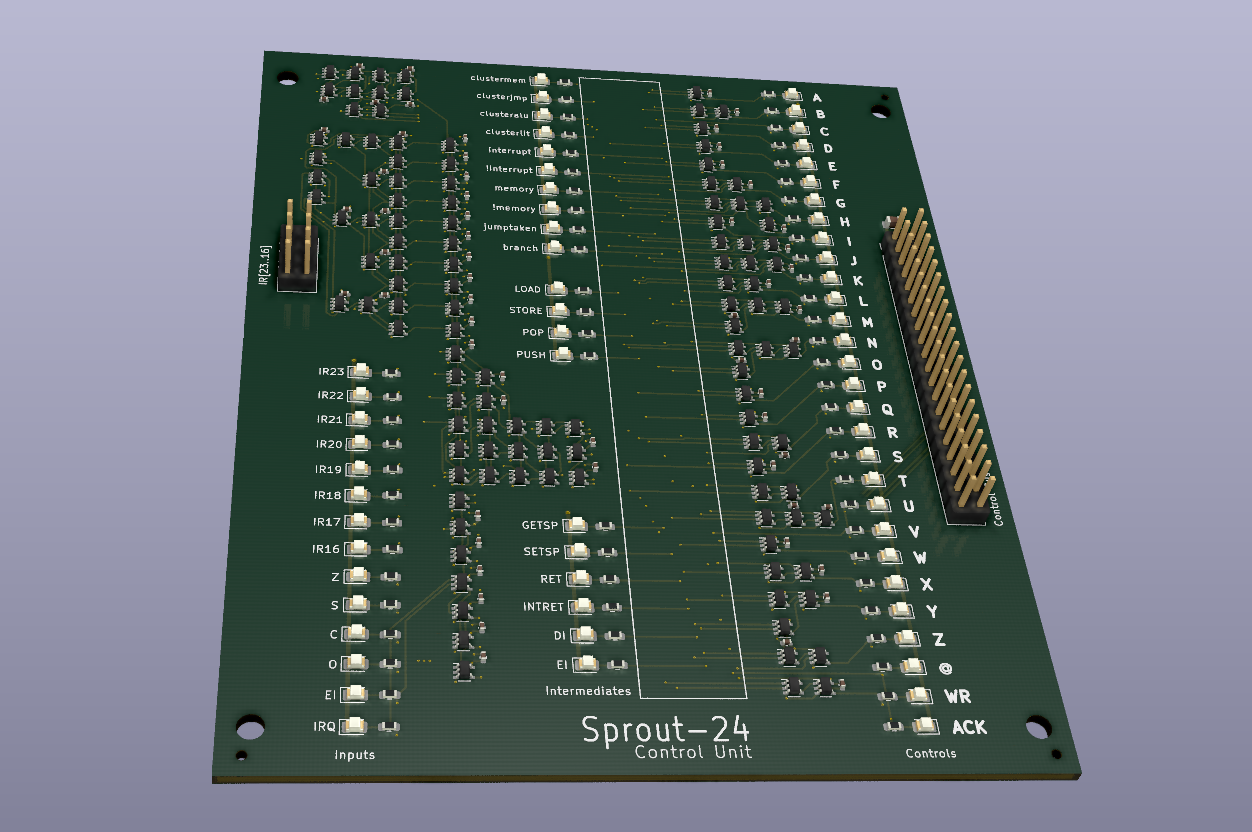

That leaves me with three open issues and no other known problems:

- Conditional jumps — needs an updated Control Unit board to select correct jump type

- Register timing — needs an updated Register File controller to latch on falling edge of clock

- Carry flag — may just need to update docs and emulator

Getting close!

January 27, 2024 — I found the reason for the conditional jumps acting all weird. The "jump taken" signal was looking at instruction bits 18–16 instead of 19–17 to determine what type of conditional jump it is. That's effectively just a transcription error when transcribing the design from emulator code to schematic. I'll need to design an updated control unit board, but I know exactly what to fix now.

January 26, 2024 — I think I've solved the register timing issue. The clock pulse idea didn't work reliably, but waiting to select the new writeback register until the second half of the clock cycle does the trick. With that out of the way, it's behaving more predictably, making it easier to isolate the remaining problems. Now I'm seeing two separate issues: first is a carry flag sometimes being set when it's not supposed to, and second appears to be an issue with the "jump taken" signal not always getting set correctly for some types of conditional jumps. I will definitely need a revision B for the RegisterFile board, and quite likely one for the Control Unit as well.

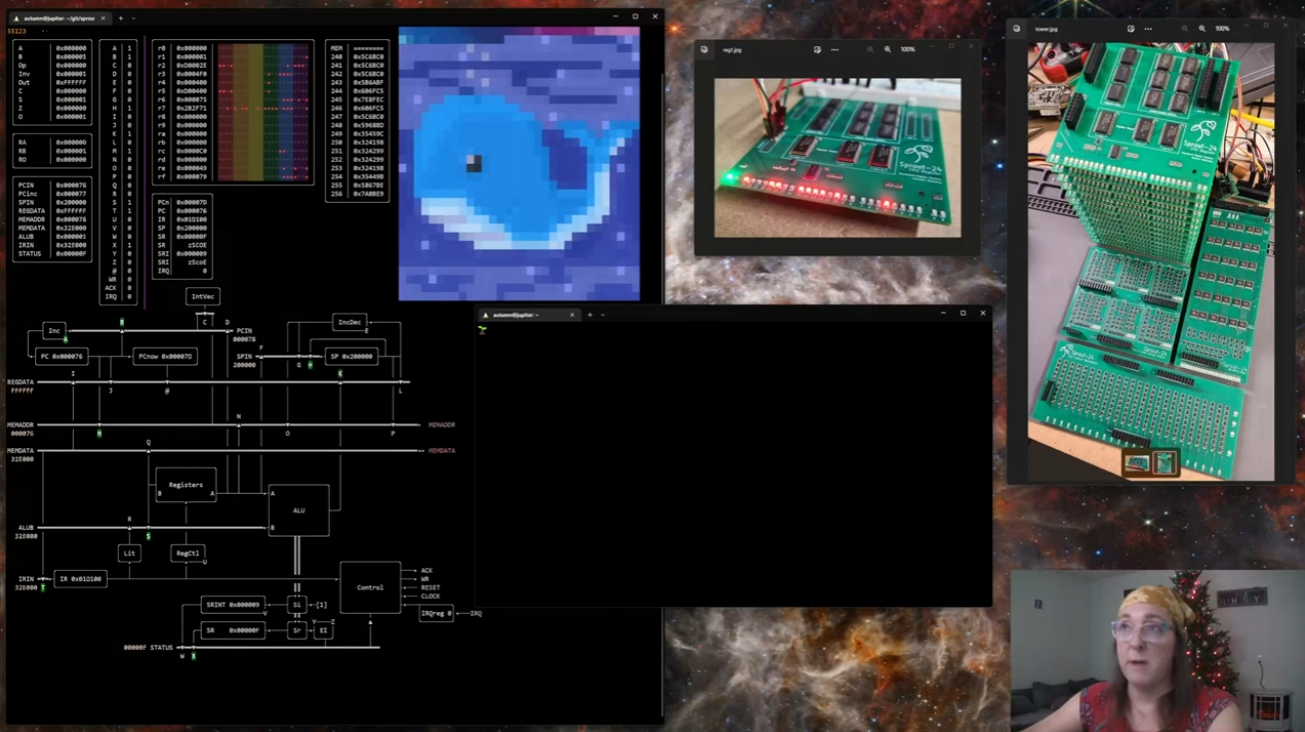

January 15, 2024 — Held an live stream while doing some testing, and ended up giving a few folks an impromptu tour at the end.

January 10, 2024 — Tracking down some issues with ALU flag values, and it looks like it may be related to the workaround that delays the clock signal going to the registers. I think the right way to solve that register clock timing issue is to instead convert the clock signal the registers see into just a quick pulse at the clock rising edge so that the write signal doesn't slew over to the next instruction's output register. Waiting on a parts order to be able to better test that theory.

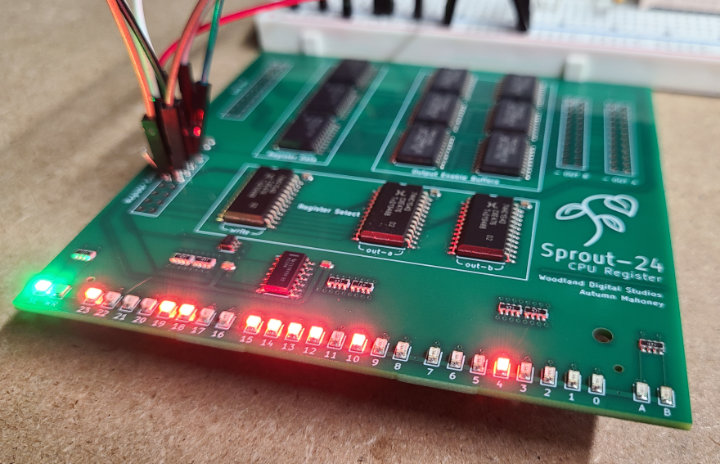

January 5, 2024 — I had some fun with my first workbench livestream tonight! I did some live troubleshooting and tracked down a bad ShiftBusReader board. Removing it from the chain allowed all the rest of them to work as expected, and results against a couple of test programs are matching up 100%. Next step is to test more complicated programs and see if conditional jumps are all working correctly.

December 12, 2023 — Oops, never mind. I just forgot to reconnect a bodge wire, so the VCPU pin on the expansion slots was dead, making the shift registers on the test interface only halfheartedly drive the memdata bus with whatever voltage leaked through them from the signal pins. Plugging the bodge wire back in immediately solved it. Phew.

December 10, 2023 — Installed the new pinadapters and backplane connector, but something along the way broke either the memdata bus or the test interface board. I think I'm going to have to tear everything apart to troubleshoot, which at this point looks like it will have to be after the holidays. Frustrating indeed after being so close.

November 27, 2023 — Ordered a revision B for the Southeast board that adds the missing IRIN pulldown and breaks out more internals to headers for automated monitoring. Created and ordered Protocard for making experimental expansion cards, Pinadapter to adapt sketchy blade pins to square pins, and Backplane Connector to replace ribbon cables between CPU and backplane.

November 21, 2023 — Testing is progressing much faster with the help of the new test interface. I've identified and worked around two hardware bugs this week — one was a clock skew issue that was allowing bad data to seep into general registers, and the other was from the IR input bus missing its pulldowns so the IR sometimes clocked garbage data during a memory-access stall cycle.

November 14, 2023 — Revised Northwest board is testing good. The backplane and test interface are working. Now to keep moving forward with extensive testing of the CPU as a whole. There is so much complexity to test, but the new test interface board will make it a lot easier than having to wire every bit of the test connections by hand.

November 7, 2023 — Backplane, debugger, and revised Northwest board have arrived.

October 30, 2023 — Placed order for the backplane, debugger, and revised Northwest board.

October 23, 2023 — Trying to debug everything is becoming more and more of a ratsnest of wires. I would eventually need to design a backplane anyway, so I just finished a basic 8-port backplane and am starting on a debugger expansion board that will interface between the backplane and a Raspberry Pi to drive the testing. The plan is to order the updated Northwest board, the backplane, and the debugger board in the same order to save on shipping.

October 13, 2023 — We had a lot of family adventures and outdoor fun over the summer. Now that it's cold outside again, I'm back to working on this project in the evenings. Tonight I created revision B of the Northwest board that fixes the lookahead carry for the PC and SP incrementors. I also updated this board from KiCAD 5 to KiCAD 7; it took a surprising amount of work to adjust for the changes that came from that.

Some quick highlights:

Load/store architecture

Word-addressing

RISC-style instruction set

53 instructions and interrupt support

Lightly pipelined

Working assembler and emulator

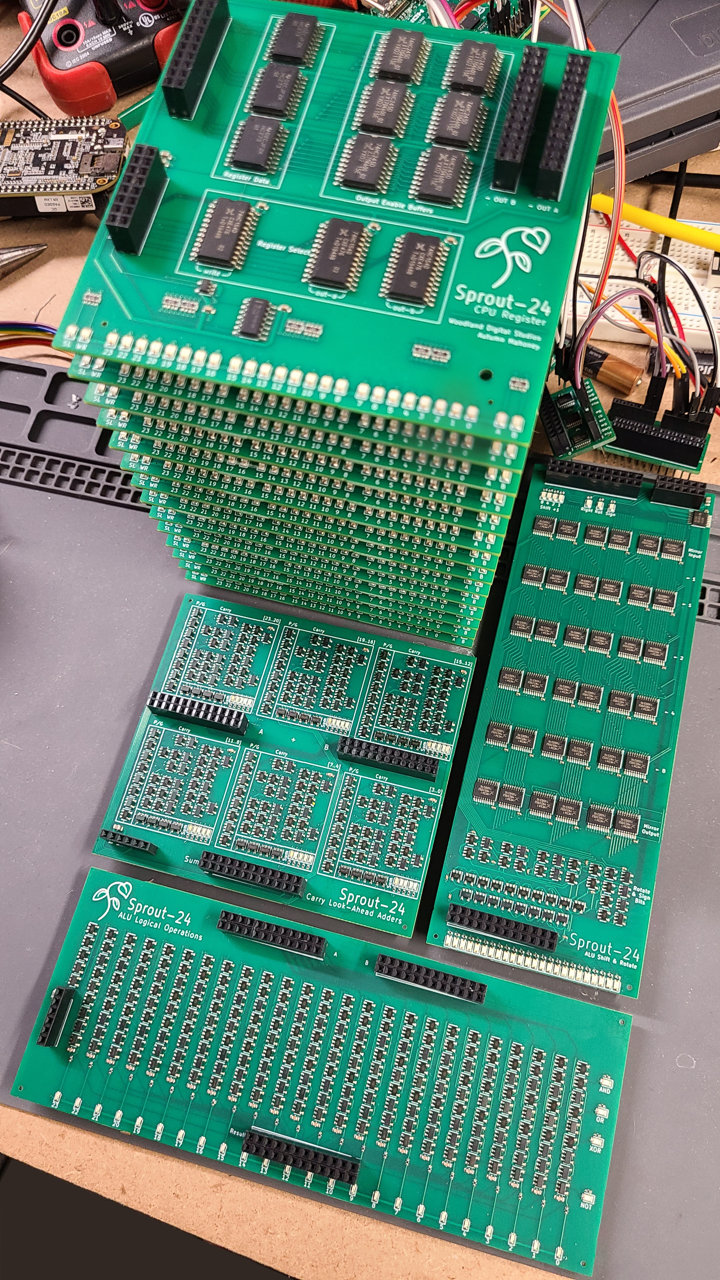

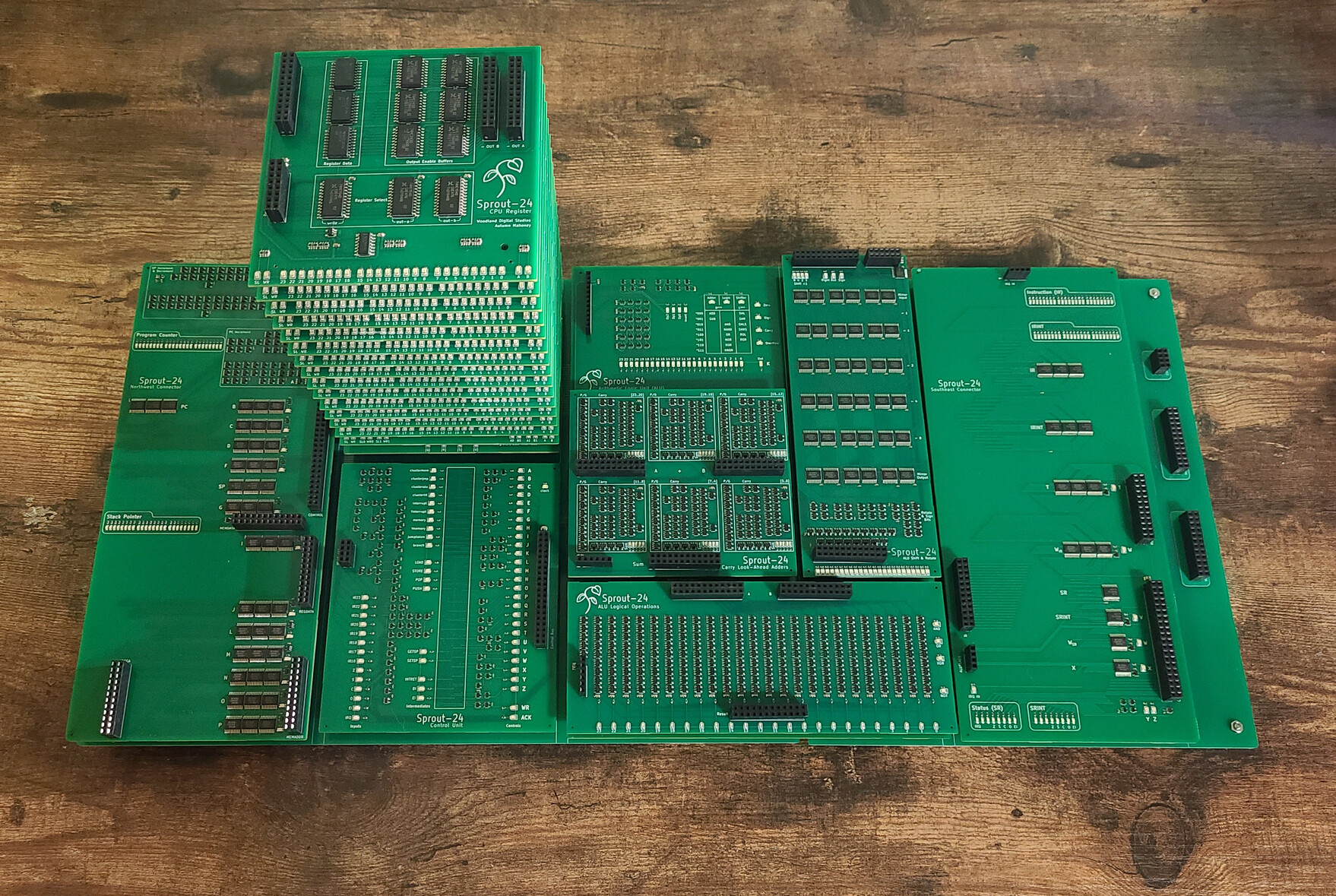

25 PCBs and 2,634 components

1,054 ICs, many of which are single logic gates

Approx. 9,700 total logic gates or 29,300 transistors

730 LEDs

I did find a design oops on the carry-lookahead adder that increments the program counter, so it goes haywire after counting to 256, but I think I will be able to bodge that to be able to finish testing.

April 4, 2023 — All boards are tested as well as they can be individually. Tonight I assembled all the boards together, and she's beautiful. I'll be powering the whole thing up and starting to test it in the coming days.

April 1, 2023 — Assembled ALU and Register 01 boards are complete and match emulator in testing. Register File and Control Unit are complete and pass spot-check testing.

March 30, 2023 — The order is in, and all 25 boards that make up the CPU are ready to test and assemble!

March 8, 2023 — Placed order for all remaining CPU boards, including the Southeast and East Bridge boards. Now we wait.

March 3, 2023 — My bank flagged the PCB order as suspicious, so I had to call them to confirm it was legit. In the meantime I noticed an omission in the Register File board, so I put the order on hold and made a revision B for the Register File and West Bridge boards. At this point, I'm close enough on the layout of the Southeast board that I'm going to wait to try the order again until I can include the Southeast and East Bridge boards too.

February 28, 2023 — The Register File, Register 01, Northwest, and West Bridge board designs are now finished, and I just placed an order for those plus the Control Unit and ALU Core boards. There will be a lot of things to test once this order shows up.

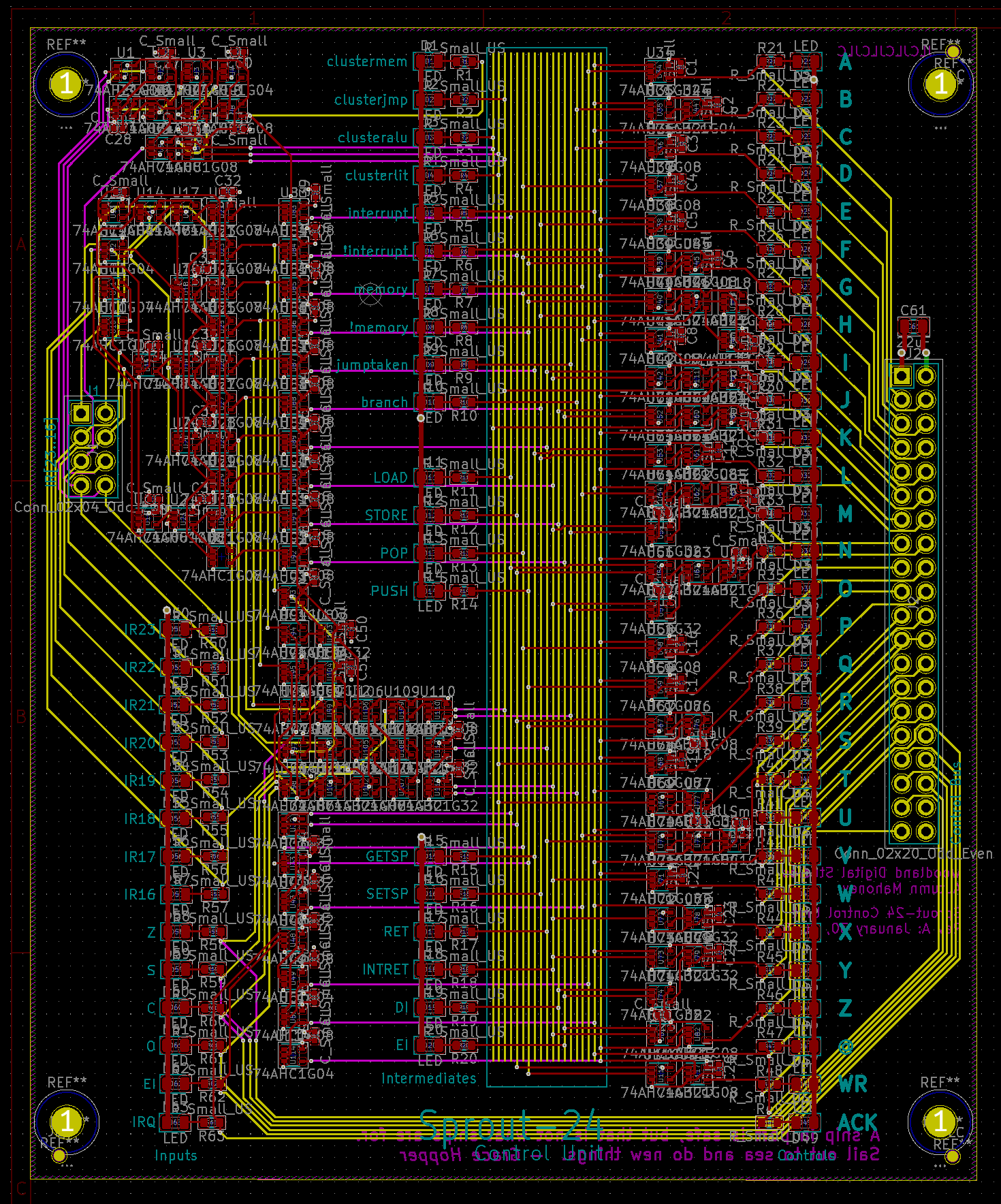

February 1, 2023 — The Control Unit and ALU Core boards are ready to order, though I'm going to wait until I have a couple others ready to save on shipping costs.

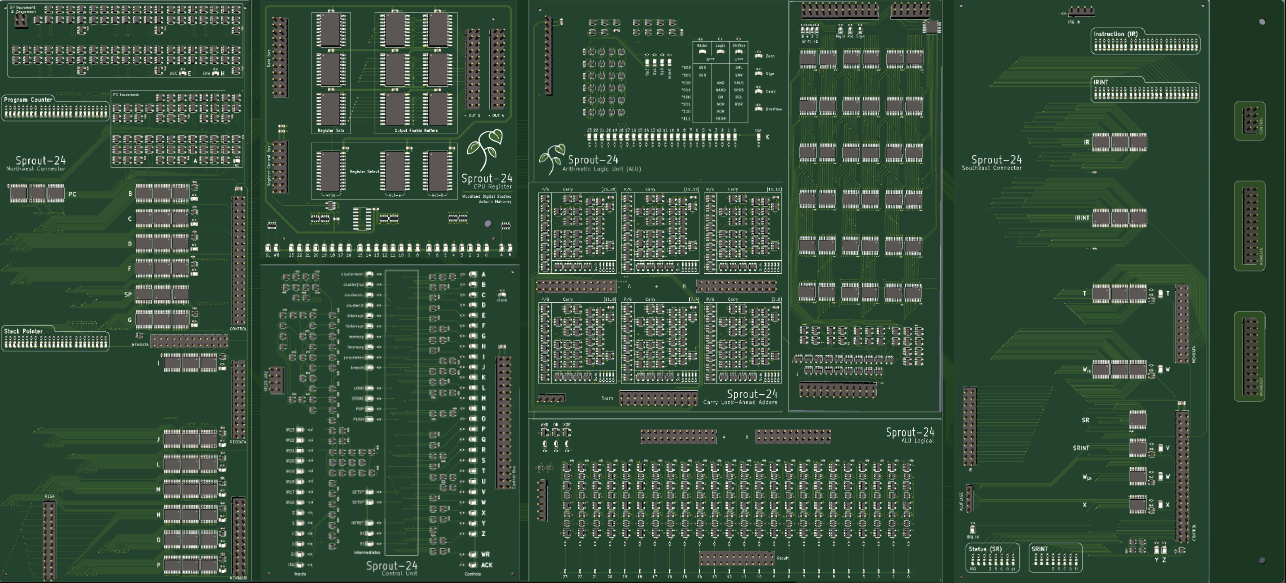

Next to design are the "Northwest" board that includes components related to the program counter and stack pointer, and the "Southeast" board that relates to the instruction and status registers.

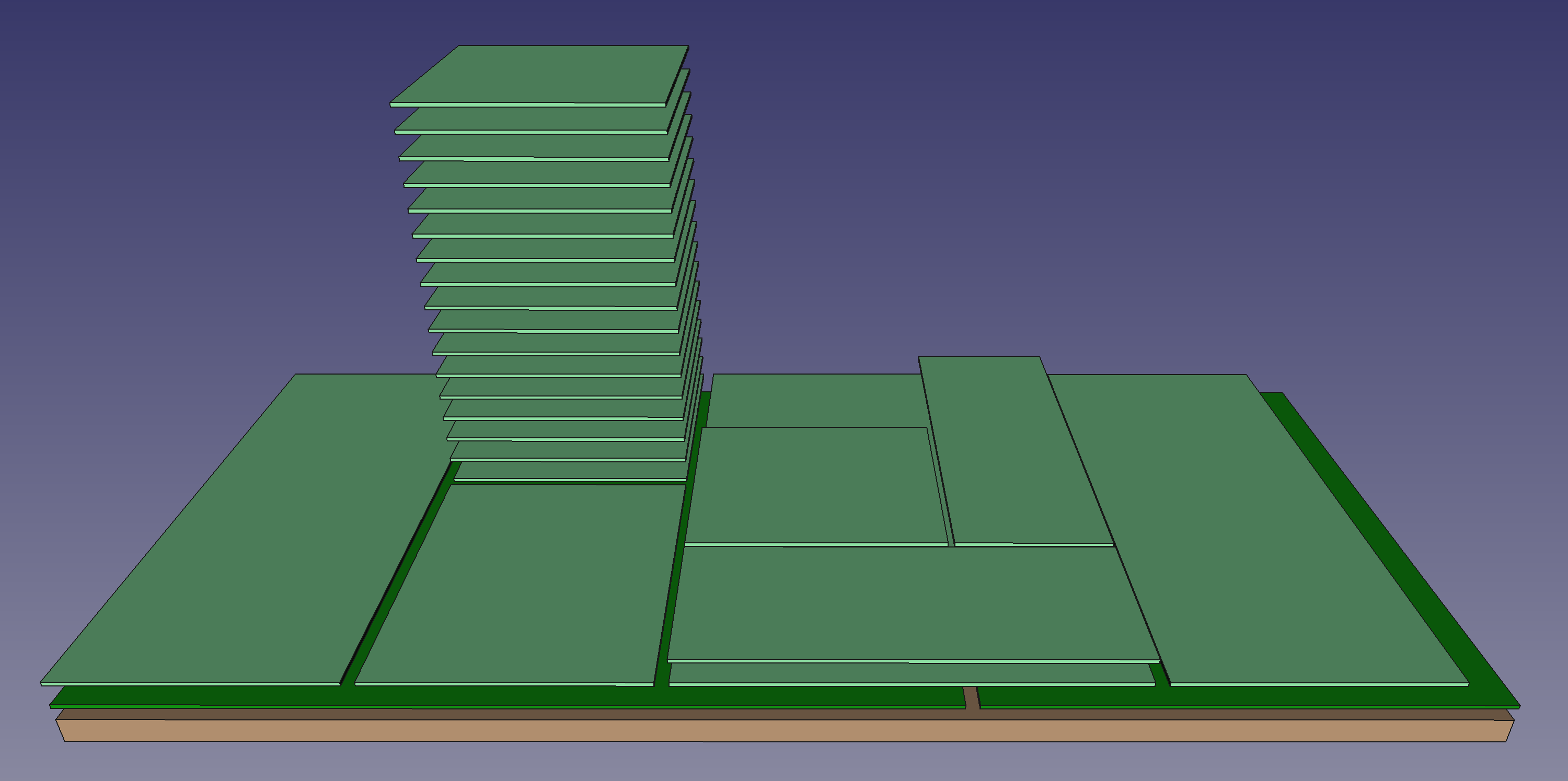

And I now have a tentative physical layout for how the individual boards will fit together into a complete CPU. Two additional helper boards with no components will sit below the rest of the boards for physical support and for routing busses between the boards above.

December 22, 2022 — The CPU's Control Unit is working and tested in the emulator, and now it's time to turn it into hardware. More details and a demo in this video.

November 22, 2021 — Ordered ALU Adder, ALU Logic, ALU Shifter, ShiftBusRead, ShiftBusWrite

October 2, 2021 — Ordered Register rev.B

March 1, 2020 — Ordered Register

February 5, 2020 — First KiCAD PCB sketch — for register board

September 27, 2019 — More design goals and ideas; sketches of board layouts

September 25, 2019 — Start of project notebook: description, what, why, first sketches of opcodes and isa, instruction encoding, register tower.

| Current Status of Circuit Boards | ||

|---|---|---|

| cpu | (rev) | |

| register | complete | B |

| register0 | revision B ready to test | B |

| registerfile | complete | B |

| alu-core | needs a rev C to fix carry flag | B |

| alu-adder | complete | A |

| alu-logic | complete | A |

| alu-shifter | complete | A |

| controlunit | complete | C |

| northwest | complete | B |

| southeast | may need a revision C to fix hold violation | B |

| westbridge | complete | B |

| eastbridge | complete | A |

| extra-cpu boards | (rev) | |

| backplane | complete, with bodge | A |

| backplane connector | complete | A |

| ram | have parts for prototype memory board | |

| rom | will initially emulate rom with a pico on a protoboard | |

| isabridge | tbd | |

| shiftbus-read | complete | A |

| shiftbus-write | complete | A |

| test interface | complete | A |

| protocard | complete | A |

| pinadapter | complete | A |

| architecture | ||

| instruction set | complete | |

| emulator | working | |

| assembler | working | |